# Lecture Notes in Computer Science

2963

Edited by G. Goos, J. Hartmanis, and J. van Leeuwen

# Springer Berlin

Berlin Heidelberg New York Hong Kong London Milan Paris Tokyo

# Higher-Level Hardware Synthesis

#### Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

Author

Richard Sharp Intel Research Cambridge 15 JJ Thomson Avenue, Cambridge, CB3 0FD, UK E-mail: richard.sharp@intel.com

Cataloging-in-Publication Data applied for

A catalog record for this book is available from the Library of Congress.

Bibliographic information published by Die Deutsche Bibliothek Die Deutsche Bibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data is available in the Internet at <a href="http://dnb.ddb.de">http://dnb.ddb.de</a>>.

CR Subject Classification (1998): B, C.1, D.2, D.3, F.3

ISSN 0302-9743 ISBN 3-540-21306-6 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag is a part of Springer Science+Business Media springeronline.com

© Springer-Verlag Berlin Heidelberg 2004 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Olgun Computergrafik Printed on acid-free paper SPIN: 10988206 06/3142 5 4 3 2 1 0

$For\ Kate$

# **Preface**

In the mid 1960s, when a single chip contained an average of 50 transistors, Gordon Moore observed that integrated circuits were doubling in complexity every year. In an influential article published by Electronics Magazine in 1965, Moore predicted that this trend would continue for the next 10 years. Despite being criticized for its "unrealistic optimism," Moore's prediction has remained valid for far longer than even he imagined: today, chips built using state-of-the-art techniques typically contain several million transistors. The advances in fabrication technology that have supported Moore's law for four decades have fuelled the computer revolution. However, this exponential increase in transistor density poses new design challenges to engineers and computer scientists alike. New techniques for managing complexity must be developed if circuits are to take full advantage of the vast numbers of transistors available.

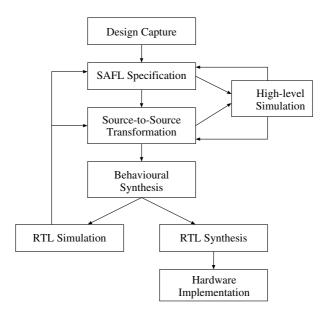

In this monograph we investigate both (i) the design of high-level languages for hardware description, and (ii) techniques involved in translating these high-level languages to silicon. We propose SAFL, a first-order functional language designed specifically for behavioral hardware description, and describe the implementation of its associated silicon compiler. We show that the high-level properties of SAFL allow one to exploit program analyses and optimizations that are not employed in existing synthesis systems. Furthermore, since SAFL fully abstracts the low-level details of the implementation technology, we show how it can be compiled to a range of different design styles including fully synchronous design and globally asynchronous locally synchronous (GALS) circuits.

We argue that one of the problems with existing high-level hardware synthesis systems is their "black-box approach": high-level specifications are translated into circuits without any human guidance. As a result, if a synthesis tool generates unsuitable designs there is very little a designer can do to improve the situation. To address this problem we show how source-to-source transformation of SAFL programs "opens the black-box," providing a common language in which users can interact with synthesis tools whilst exploring the different architectural tradeoffs arising from a single SAFL specification. We demonstrate this design methodology by presenting a number of transformations that facili-

#### VIII Preface

tate resource-duplication/sharing and hardware/software co-design as well as a number of scheduling and pipelining tradeoffs.

Finally, we extend the SAFL language with (i)  $\pi$ -calculus style channels and channel-passing, and (ii) primitives for *structural*-level circuit description. We formalize the semantics of these languages and present results arising from the generation of real hardware using these techniques.

This monograph is a revised version of my Ph.D. thesis which was submitted to the University of Cambridge Computer Laboratory and accepted in 2003. I would like to thank my supervisor, Alan Mycroft, who provided insight and direction throughout, making many valuable contributions to the research described here. I am also grateful to the referees of my thesis, Tom Melham and David Greaves, for their useful comments and suggestions. The work presented in this monograph was supported by (UK) EPSRC grant GR/N64256 "A Resource-Aware Functional Language for Hardware Synthesis" and AT&T Research Laboratories Cambridge.

December 2003 Richard Sharp

# Contents

| 1        | Int            | roduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1  |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|          | 1.1            | Hardware Description Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1  |

|          | 1.2            | Hardware Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7  |

|          |                | 1.2.1 High-Level Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8  |

|          | 1.3            | Motivation for Higher Level Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14 |

|          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14 |

|          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15 |

|          | 1.4            | Structure of the Monograph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16 |

| <b>2</b> | $\mathbf{Rel}$ | ated Work 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19 |

|          | 2.1            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19 |

|          | 2.2            | o contract of the contract of | 23 |

|          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23 |

|          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25 |

|          |                | 2.2.3 Hebe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25 |

|          | 2.3            | Functional Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26 |

|          |                | 2.3.1 $\mu$ FP: An Algebra for VLSI Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26 |

|          |                | 2.3.2 Embedding HDLs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|          |                | in General-Purpose Functional Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28 |

|          | 2.4            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30 |

|          | 2.5            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31 |

|          |                | 2.5.1 Handel and Handel-C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31 |

|          |                | 2.5.2 Tangram and Balsa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31 |

|          | 2.6            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33 |

|          | 2.7            | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34 |

| 3        | The            | e SAFL Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35 |

|          | 3.1            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35 |

|          | 3.2            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 36 |

|          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 37 |

|          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 37 |

|          |                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38 |

| v | 0        |

|---|----------|

| X | Contents |

|   |      | 3.2.4 Concrete Syntax                                | 38       |

|---|------|------------------------------------------------------|----------|

|   | 3.3  | Hardware Synthesis Using SAFL                        | 41       |

|   |      | 3.3.1 Automatic Generation of Parallel Hardware      | 42       |

|   |      | 3.3.2 Resource Awareness                             | 42       |

|   |      | 3.3.3 Source-Level Program Transformation            | 44       |

|   |      | 3.3.4 Static Analysis and Optimisation               | 47       |

|   |      | 3.3.5 Architecture Independence                      | 48       |

|   | 3.4  | Aside: Dealing with Mutual Recursion                 | 48       |

|   |      | 3.4.1 Eliminating Mutual Recursion by Transformation | 49       |

|   | 3.5  | Related Work                                         | 50       |

|   | 3.6  | Summary                                              | 50       |

|   |      |                                                      |          |

| 4 | Soft | Scheduling                                           | 51       |

|   | 4.1  | Motivation and Related Work                          | 52       |

|   |      | 4.1.1 Translating SAFL to Hardware                   | 54       |

|   | 4.2  | Soft Scheduling: Technical Details                   | 55       |

|   |      | 4.2.1 Removing Redundant Arbiters                    | 56       |

|   |      | 4.2.2 Parallel Conflict Analysis (PCA)               | 56       |

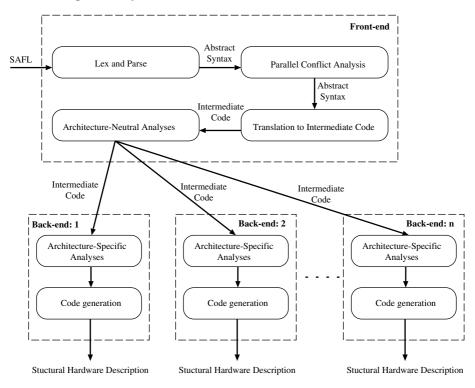

|   |      | 4.2.3 Integrating PCA into the FLaSH Compiler        | 58       |

|   | 4.3  | Examples and Discussion                              | 58       |

|   |      | 4.3.1 Parallel FIR Filter                            | 58       |

|   |      | 4.3.2 Shared-Memory Multi-processor Architecture     | 59       |

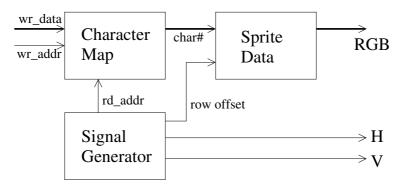

|   |      | 4.3.3 Parallel Tasks Sharing Graphical Display       | 61       |

|   | 4.4  | Program Transformation for Scheduling and Binding    | 62       |

|   | 4.5  | Summary                                              | 63       |

|   |      |                                                      |          |

| 5 |      | h-Level Synthesis of SAFL                            | 65       |

|   | 5.1  | FLaSH Intermediate Code                              | 66       |

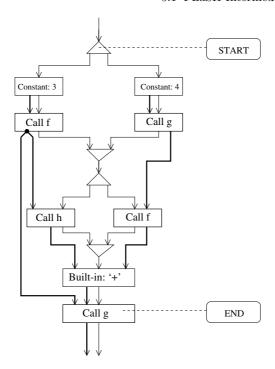

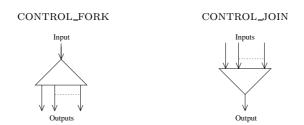

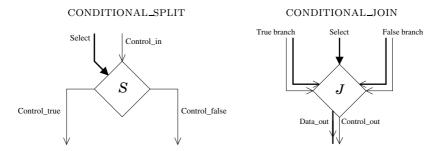

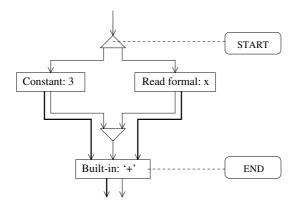

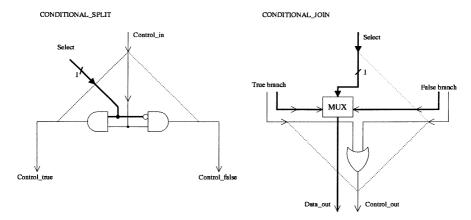

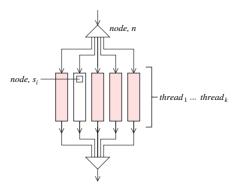

|   |      | 5.1.1 The Structure of Intermediate Graphs           | 67       |

|   |      | 5.1.2 Translation to Intermediate Code               | 71       |

|   | 5.2  | Translation to Synchronous Hardware                  | 73       |

|   |      | 5.2.1 Compiling Expressions                          | 73       |

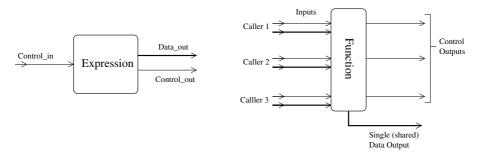

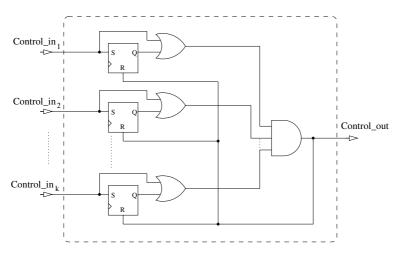

|   |      | 5.2.2 Compiling Functions                            | 75       |

|   |      | 5.2.3 Generated Verilog                              | 79       |

|   |      | 5.2.4 Compiling External Functions                   | 80       |

|   | 5.3  | Translation to GALS Hardware                         | 81       |

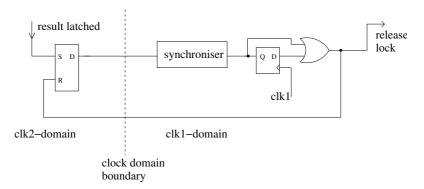

|   |      | 5.3.1 A Brief Discussion of Metastability            | 81       |

|   |      | 5.3.2 Interfacing between Different Clock Domains    | 83       |

|   |      | 5.3.3 Modifying the Arbitration Circuitry            | 85       |

|   | 5.4  | Summary                                              | 86       |

| 6 | 1 22 | dysis and Optimisation of Intermediate Code          | 87       |

| U | 6.1  | Architecture-Neutral verses Architecture-Specific    | 87       |

|   | 6.2  | Definitions and Terminology                          |          |

|   |      | Register Placement Analysis and Optimisation         | 88       |

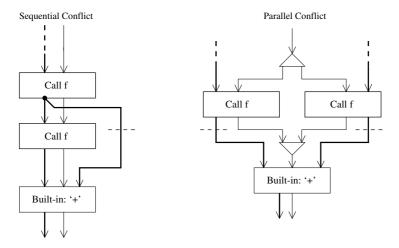

|   | 6.3  | 6.3.1 Sharing Conflicts                              | 88<br>89 |

|   |      | D.A. L. ADSTING COUNTYS                              | 24       |

|   |     |                                |                                         | Contents | XI    |

|---|-----|--------------------------------|-----------------------------------------|----------|-------|

|   |     | 6.3.2 Technical Details        | • • • • • • • • • • • • • • • • • • • • |          | 91    |

|   |     | 6.3.3 Resource Dependency A    | analysis                                |          | . 92  |

|   |     | 6.3.4 Data Validity Analysis   |                                         |          |       |

|   |     | 6.3.5 Sequential Conflict Reg  |                                         |          |       |

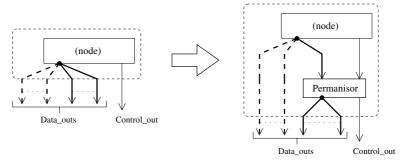

|   | 6.4 | Extending the Model: Calling   |                                         |          |       |

|   |     | 6.4.1 Caller-Save Resource De  |                                         |          |       |

|   |     | 6.4.2 Caller-Save Permanisati  |                                         |          |       |

|   | 6.5 | Synchronous Timing Analysis    |                                         |          |       |

|   |     | 6.5.1 Technical Details        |                                         |          | 100   |

|   |     | 6.5.2 Associated Optimisation  | ns                                      |          | 101   |

|   | 6.6 | Results and Discussion         |                                         |          | 104   |

|   |     | 6.6.1 Register Placement Ana   | alysis: Results                         |          | 104   |

|   |     | 6.6.2 Synchronous Timing Op    | otimisations: Results .                 |          | 109   |

|   | 6.7 | Summary                        | • • • • • • • • • • • • • • • • • • • • |          | . 110 |

|   |     | •                              |                                         |          |       |

| 7 |     | dling with I/O                 |                                         |          |       |

|   | 7.1 | SAFL+ Language Description     |                                         |          |       |

|   |     | 7.1.1 Resource Awareness       |                                         |          |       |

|   |     | 7.1.2 Channels and Channel     |                                         |          |       |

|   |     | 7.1.3 The Motivation for Cha   | _                                       |          |       |

|   | 7.2 | Translating SAFL+ to Hardwa    |                                         |          |       |

|   |     | 7.2.1 Extending Analyses from  |                                         |          |       |

|   | 7.3 | Operational Semantics for SAF  |                                         |          |       |

|   |     | 7.3.1 Transition Rules         |                                         |          |       |

|   |     | 7.3.2 Semantics for Channel l  |                                         |          |       |

|   |     | 7.3.3 Non-determinism          |                                         |          |       |

|   | 7.4 | Summary                        |                                         |          | . 126 |

| 8 | Cor | nbining Behaviour and Stru     | cture                                   |          | 120   |

| 0 | 8.1 | Motivation and Related Work    |                                         |          |       |

|   | 8.2 | Embedding Structural Expansi   |                                         |          |       |

|   | 0.2 | 8.2.1 Building Combinatorial   |                                         |          |       |

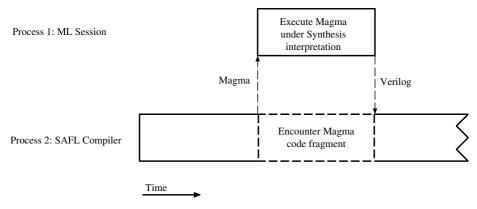

|   |     | 8.2.2 Integrating SAFL and M   |                                         |          |       |

|   | 8.3 | Aside: Embedding Magma in V    |                                         |          |       |

|   | 8.4 | Summary                        |                                         |          |       |

|   |     | •                              |                                         |          |       |

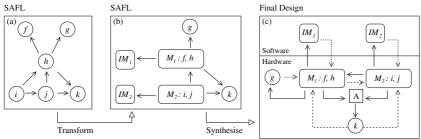

| 9 |     | nsformation of SAFL Specif     |                                         |          |       |

|   | 9.1 | Hardware Software CoDesign     |                                         |          |       |

|   |     | 9.1.1 Comparison with Other    |                                         |          |       |

|   | 9.2 | Technical Details              |                                         |          |       |

|   |     | 9.2.1 The Stack Machine Ten    | _                                       |          |       |

|   |     | 9.2.2 Stack Machine Instance   |                                         |          |       |

|   |     | 9.2.3 Compilation to Stack C   |                                         |          |       |

|   |     | 9.2.4 The Partitioning Transf  |                                         |          |       |

|   |     | 9.2.5 Validity of Partitioning |                                         |          |       |

|   |     | 9.2.6 Extensions               |                                         |          | . 149 |

|              | 9.3 Transformations from SAFL to SAFL+       151         9.4 Summary       153                                                                                                                                |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

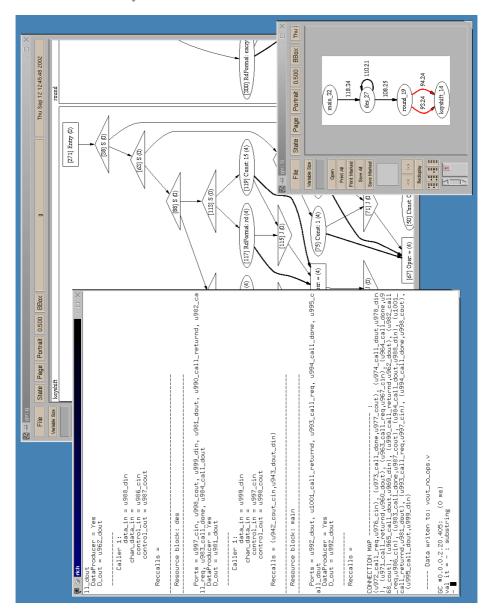

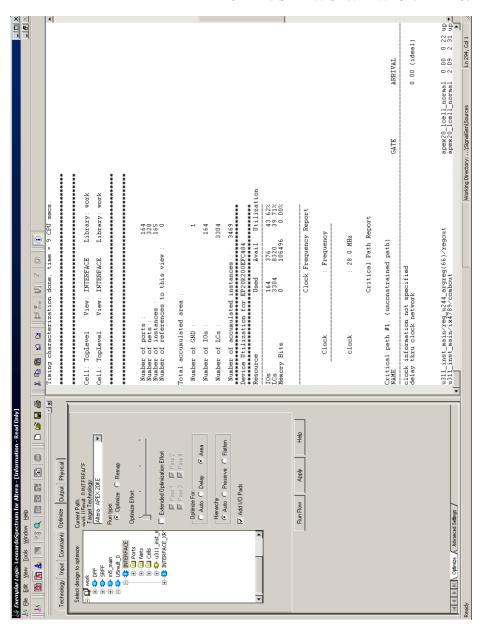

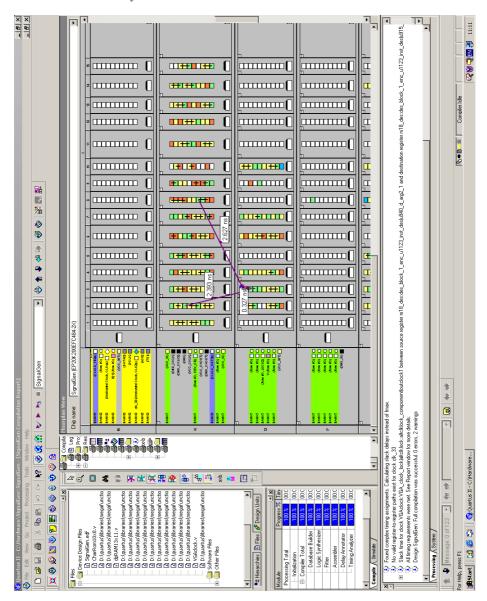

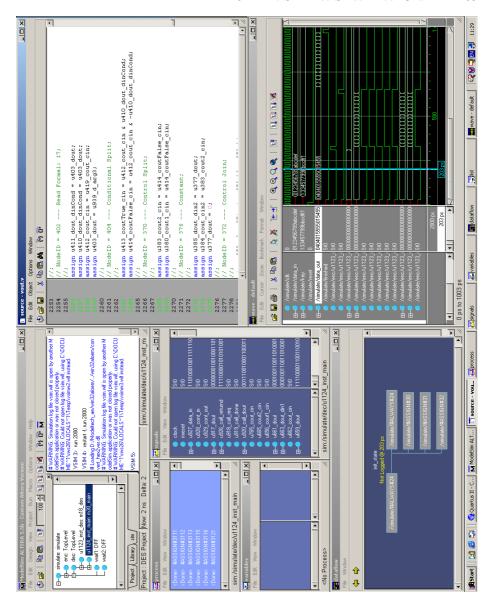

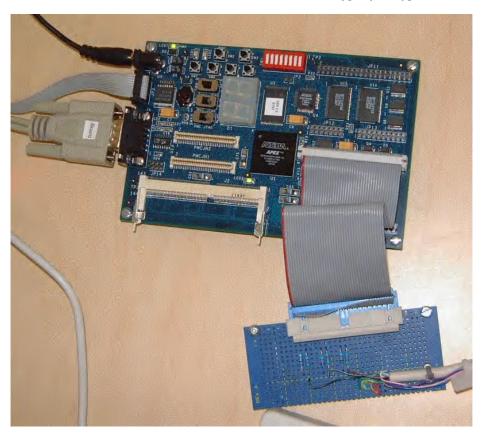

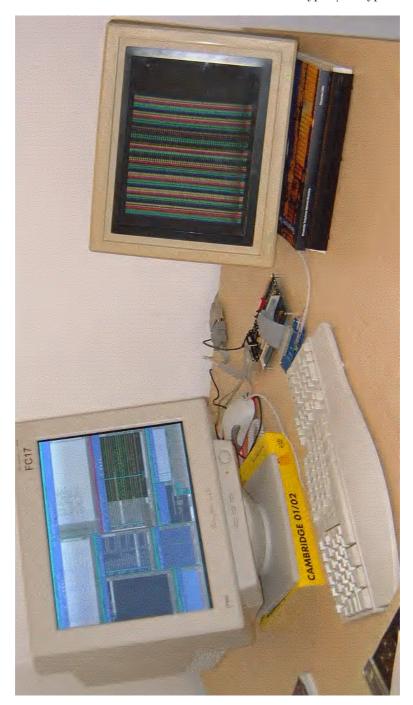

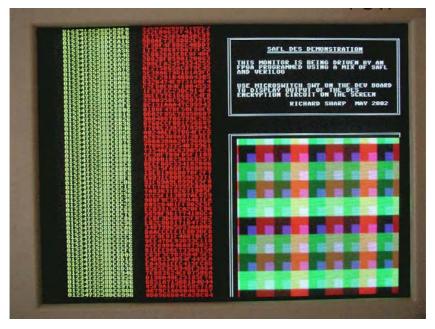

| 10           | Case Study       155         10.1 The SAFL to Silicon Tool Chain       155         10.2 DES Encrypter/Decrypter       160         10.2.1 Adding Hardware VGA Support       162         10.3 Summary       167 |

| 11           | Conclusions and Further Work                                                                                                                                                                                  |

| Аp           | endix                                                                                                                                                                                                         |

| A            | DES Encryption/Decryption Circuit                                                                                                                                                                             |

| В            | Transformations to Pipeline DES                                                                                                                                                                               |

| $\mathbf{C}$ | A Simple Stack Machine and Instruction Memory 181                                                                                                                                                             |

|              |                                                                                                                                                                                                               |

| Re           | rences                                                                                                                                                                                                        |

# List of Figures